BETA Protecting

SITOR Semiconductor Fuses

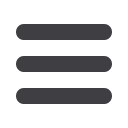

SITOR, LV HRC design

4/16

Siemens ET B1 · 10/2008

4

3

NC5 531

3

NC5 8. .

3

NE6 4. .-7, 3NE9 4. .-7

3

NE6 4. ., 3NE9 4. .

M10

M10

SW41

91

9

24,5

0,3

I2_11369a

Ø

50

Ø

50

Ø

28

M10

M24

M10

SW41

b

a

c

11

I2_11370a

Ø

73

Ø

40

70

M10

70

100

125

83

10

10

81,5

75,5

I2_11372a

Ø

11

Ø

28

10

70

M10

70

b

a

10

81,5

I2_11371a

Ø

28

Type

Dimensions (mm)

a

b

c

3

NC5 838

98

88.5

25

3

NC5 841

98

88.5

25

3

NC5 840

119

109.5 20.5

Type

Dimensions (mm)

a

b

3

NE6 437

89

76

3

NE9 450

89

76

3

NE9 440-6

89

76

3

NE6 444

99

86

3

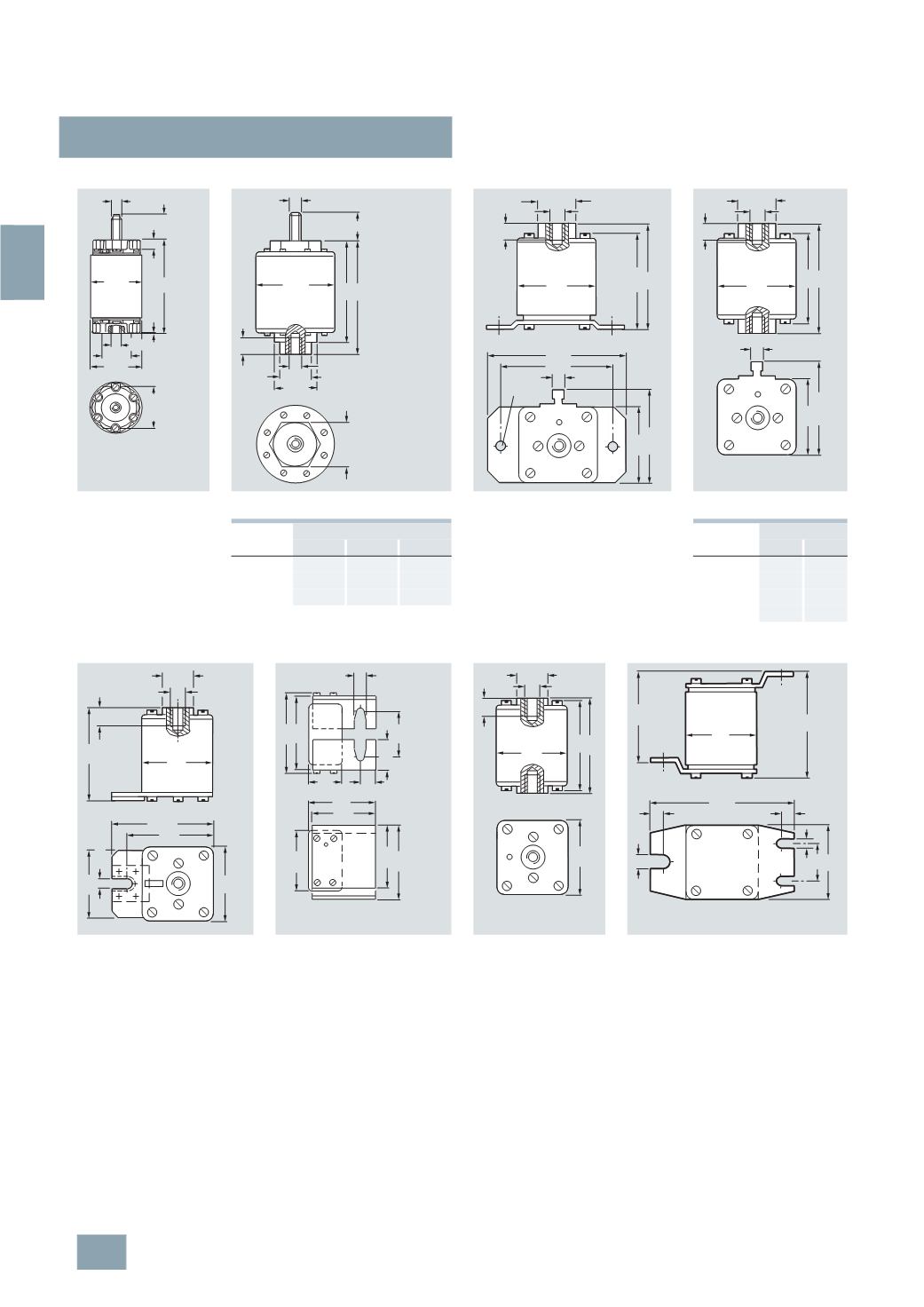

NE3 . . .-5

3

NE4 1. .-5

3

NE4 3. .-6B, 3NE4 337-6 3NC7 3. .-2

77

55

15

60

73

60

M10

10,5

82,5

I2_11373a

Ø

20

66

47

52

53

30 10

54

57

62

26

40

10,4

I2_11375a

I2_11374a

60

M10

60

76

15

77

Ø

20

12,5

57

68

119

57

30

7

79

10,5

10,5

I2_11376a

© Siemens AG 2008