BETA Protecting

SITOR Semiconductor Fuses

SITOR, LV HRC design

4/15

Siemens ET B1 · 10/2008

4

3

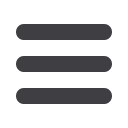

NE5 6. .-0C

3

NE5 4. .-0C, 3NE5 4. .-1C;

3

NE7 . . .-0C, 3NE7 . . .-1C

3

NE9 6. .-1C

Type

Dimensions (mm)

Type

Dimensions (mm)

a b c d e

a

3

NE5 6. .-0C

201 169 121 131.5 11.5

3

NE5 4. .-0C

11.5

3

NE5 4. .-1C

13

3

NE7 . . .-0C

11.5

3

NE7 . . .-1C

13

18

e

d

b

18

32

e

c

a

Ø

75

6

17,6

59,4

9

10

19

I2_13723

18

a

171,5

209

18

32

a

161

241

Ø

75

6

17,6

59,4

9

10

19

I2_13724a

18

13

219,5

257

18

32

13

208,5

289

Ø

75

6

17,6

59,4

9

10

19

I2_13725a

© Siemens AG 2008