BETA Protecting

SITOR Semiconductor Fuses

SITOR, LV HRC design

4/11

Siemens ET B1 · 10/2008

4

■

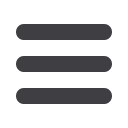

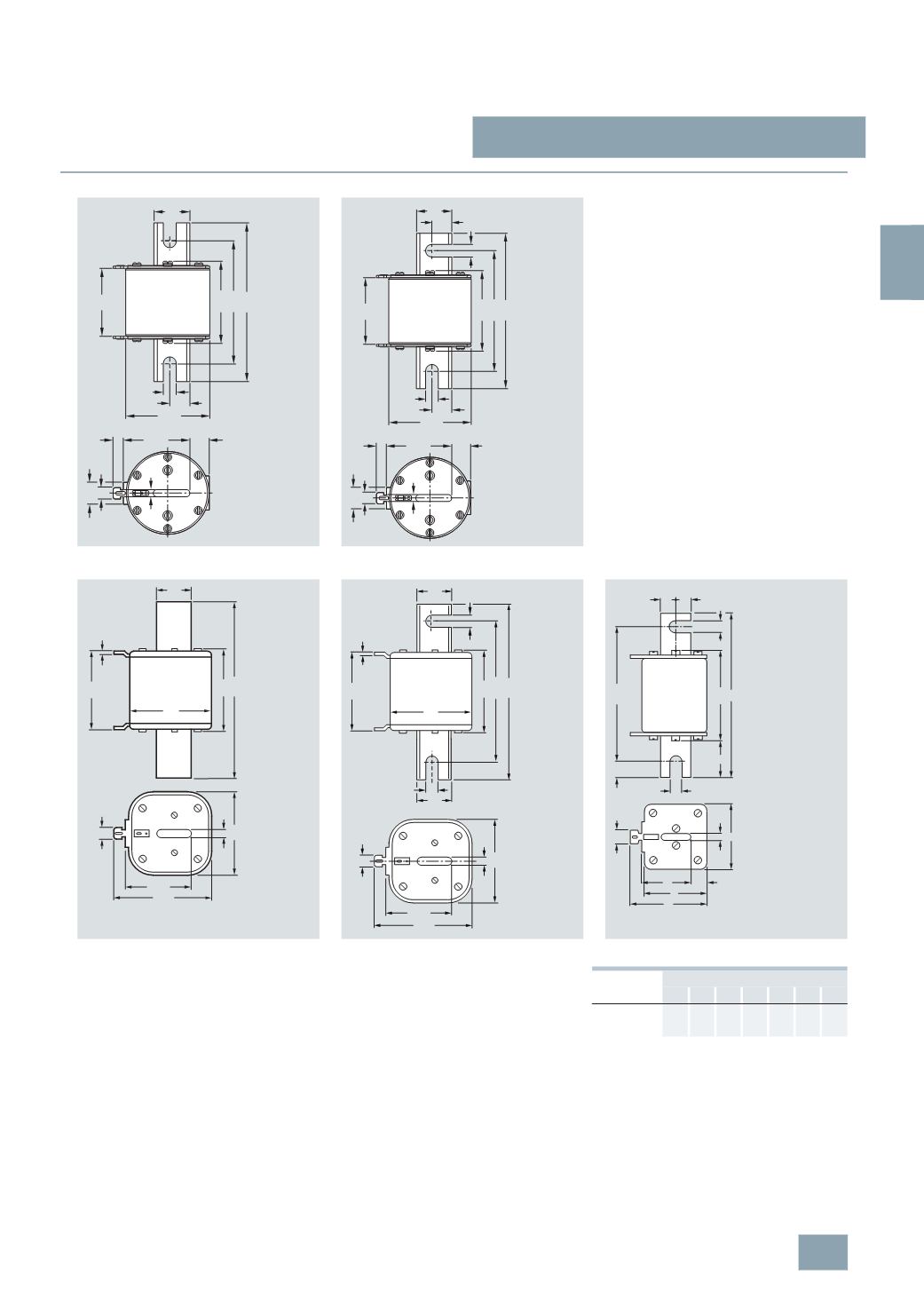

Dimensional drawings

3

NC2 4. .-0C, 3NC8 4. .-0C

3

NC2 4. .-3C, 3NC8 4. .-3C

3

NE1 43.-0, 3NE1 43.-1

3

NE1 4. .-3

3

NE1 2. .-3, 3NE1 3. .-3

Type

Dimensions (mm)

a b c d e f

g

3

NE1 2. .-3

135 31 12.5 40.5 13.5 52 63.5

3

NE1 3. .-3

149 38 19.5 47.5 15 60 72

18

11,5

71,5

109

32

61

141

Ø

75

6

17,6

59,4

9

10

19

I2_13719a

18

11,5

11,5

71,5

109

18

32

61

141

Ø

75

6

17,6

59,4

9

10

19

I2_13721a

70

151

I2_06717

10

6

60,4

82,1

68

2,5

73

70

32

70

151

I2_13936

10

6

60,4

82,1

68

2,5

73

70

32

13

13

110

32

I2_06473b

10

73

10,5

110

12,512,5

10,5

d e

f

g

a

f

c

b

6

© Siemens AG 2008