BETA Protecting

SITOR Semiconductor Fuses

SITOR, LV HRC design

4/12

Siemens ET B1 · 10/2008

4

3

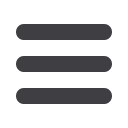

NE8 7. .-1

3

NE1 8. .-0

3

NE1 02.-0, 3NE1 02.-2, 3NE8 0. .-1

3

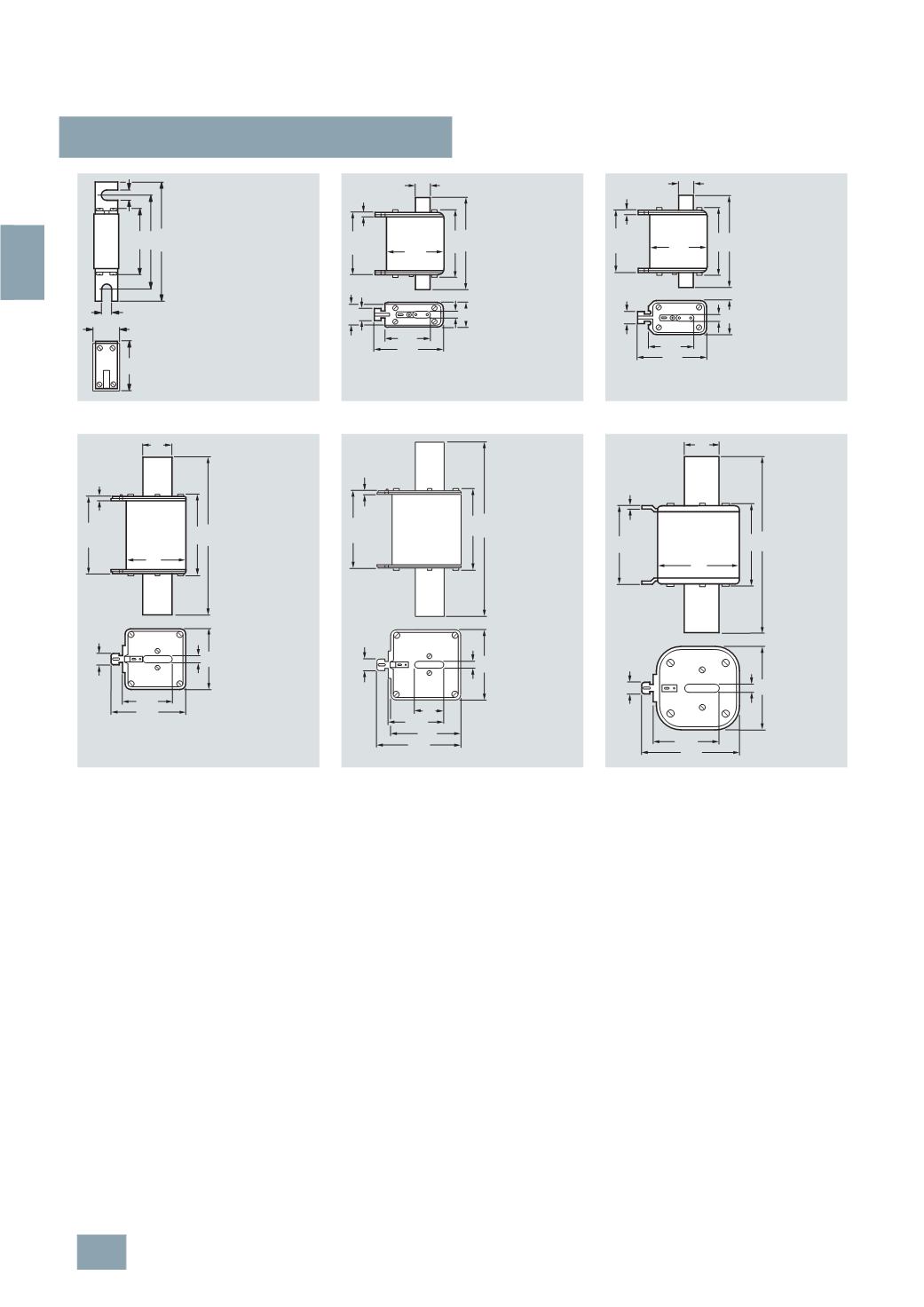

NE1 2. .-0, 3NE1 2. .-2

3

NE1 33.-0, 3NE1 33.-2

3

NE1 4. .-2

8,5

8,5

78

100

54

I2_11343

21

40

6

79,9

50,3

2,3

I2_06713

10

53,3

20

35,8

15

21

40,5

53,8

53

49,4

2,2

10

I2_06714

6

48

30

79

60

35,8

15

10

40,5

52

52

73

66,5

3

I2_06715

25

63,5

6

135

I2_07071

47,5

25

72

60

60

6

10

66,5

3

73

149

© Siemens AG 2008